I2C sběrnice — přiřazení, zařízení, přenos dat, adresování

Při vytváření elektronického obvodu se mnoho vývojářů potýká s nutností použít velké množství mezilehlých čipů pro párování, vzorkování a adresování jeho jednotlivých bloků. Aby se minimalizoval počet pomocných čipů, navrhl Philips již v 80. letech dvoudrátové obousměrné sériové síťové rozhraní I2C, navržené speciálně pro správu více čipů v jednom zařízení.

Dnes společnost Philips sama vyrábí více než sto zařízení kompatibilních s I2C pro elektronická zařízení s nejrůznějšími účely: paměti, systémy video procesorů, analogově-digitální a digitálně-analogové převodníky, ovladače displeje atd.

Sběrnice I2C je modifikací protokolu sériové výměny dat, který je schopen přenášet sériová 8bitová data v obvyklém „rychlém“ režimu rychlostí 100 až 400 kbps. Proces výměny dat je zde realizován pouze na dvou vodičích (nepočítáme-li společný vodič): lince SDA pro data a lince SCL pro synchronizaci.

Sběrnice se stává obousměrnou díky skutečnosti, že kaskády výstupů zařízení připojených ke sběrnici mají otevřené kolektory nebo kanály, čímž se replikuje vedení AND. Výsledkem je, že sběrnice minimalizuje počet spojení mezi čipy a ponechává na desce méně požadovaných pinů a stop. Díky tomu se samotná deska ukazuje jako jednodušší, kompaktnější a technologicky vyspělejší ve výrobě.

Tento protokol umožňuje deaktivovat dekodéry adres a další externí logiku vyjednávání. Počet čipů, které mohou současně pracovat na sběrnici I2C, je omezen její kapacitou — maximálně 400 pF.

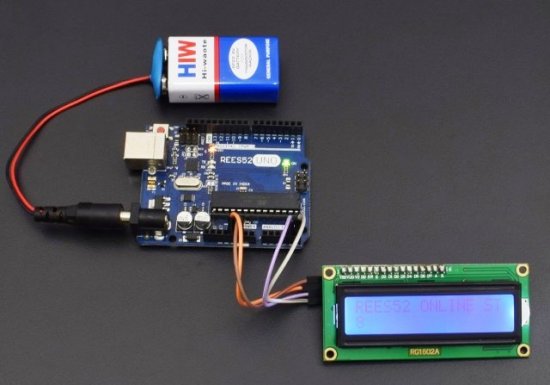

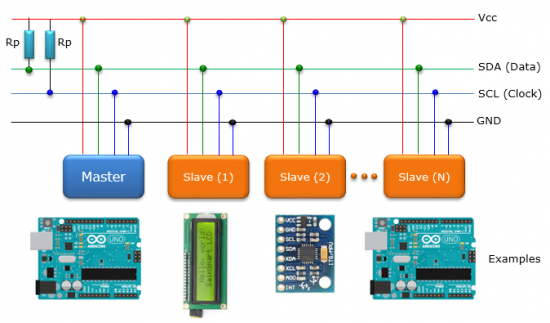

Integrované obvody kompatibilní s I2C mají algoritmus hardwarového potlačení šumu, který zajišťuje integritu dat i v přítomnosti silného rušení. Taková zařízení mají rozhraní, které umožňuje mikroobvodům vzájemně komunikovat, i když se jejich napájecí napětí liší. Na obrázku níže se můžete seznámit s principem připojení několika mikroobvodů přes společnou sběrnici.

Každé ze zařízení připojených na sběrnici má svou unikátní adresu, je jí určena a v souladu s určením zařízení může fungovat jako přijímač nebo jako vysílač. Při přenosu dat mohou být tato zařízení master (master) nebo slave (slave). Master je zařízení, které zahajuje přenos dat a generuje hodinové signály na lince SCL. Slave je ve vztahu k masteru cílové zařízení.

V každém daném okamžiku provozu na sběrnici I2C může pouze jedno zařízení fungovat jako hlavní; generuje signál na lince SCL.Master může být buď hlavní přijímač nebo hlavní vysílač.

Sběrnice v zásadě umožňuje několik různých masterů, ale ukládá omezení na charakteristiky vytváření řídicích signálů a monitorování stavu sběrnice; to znamená, že několik masterů může začít vysílat současně, ale konflikty tohoto druhu jsou eliminovány díky arbitráži, tedy způsobu, jakým se master chová, když detekuje obsazení sběrnice jiným masterem.

Synchronizace dvojice zařízení je zajištěna tím, že všechna zařízení jsou připojena na sběrnici tvořící vodič "AND". Zpočátku jsou signály SDA a SCL vysoké.

START a STOP

Výměna začíná tím, že master generuje stav «START»: na lince SDA signál přechází z vysokého do nízkého stavu, zatímco linka SCL má stabilní vysokou úroveň. Všechna zařízení připojená ke sběrnici vnímají tuto situaci jako příkaz ke spuštění ústředny.

Každý master generuje individuální hodinový signál na lince SCL při přenosu dat na sběrnici.

Výměna končí vytvořením stavu STOP masterem: na lince SDA se signál mění z nízké na vysokou, zatímco linka SCL má stabilně vysokou úroveň.

Řidič vždy vystupuje jako zdroj signálů START a STOP. Jakmile je signál «START» pevný, znamená to, že linka je obsazená. Linka je volná, když je detekován signál STOP.

Ihned po deklaraci stavu START přepne master linku SCL na nízkou úroveň a odešle nejvýznamnější bit prvního bajtu zprávy na linku SDA. Počet bajtů ve zprávě není omezen.Změny na lince SDA jsou povoleny pouze tehdy, když je úroveň signálu na lince SCL nízká. Data jsou platná a neměla by být měněna pouze v případě, že je synchronizační impuls vysoký.

Potvrzení, že bajt z hlavního vysílače byl přijat podřízeným přijímačem, se provádí nastavením speciálního potvrzovacího bitu na SDA lince po přijetí osmého datového bitu.

POTVRZENÍ

Takže odeslání 8 bitů dat z vysílače do přijímače skončí dalším impulsem na lince SCL, když přijímací zařízení klesne na lince SDA, což znamená, že přijalo celý bajt.

Potvrzení je nedílnou součástí procesu přenosu dat. Master generuje synchronizační impuls. Vysílač odešle do SDA nízký stav, zatímco jsou aktivní hodiny potvrzení. Zatímco je synchronizační puls vysoký, přijímač musí udržovat SDA na nízké úrovni.

Pokud cílový slave nepotvrdí svou adresu, například proto, že je právě obsazený, musí být datová linka udržována vysoko. Master pak může dát signál STOP k přerušení odeslání.

Pokud je příjem realizován nadřízeným přijímačem, pak je povinen informovat podřízený vysílač po dokončení přenosu - nikoliv potvrzením posledního bajtu. Podřízený vysílač uvolní datové vedení, takže master může vydat signál STOP nebo opakující se signál START.

Synchronizace zařízení je zajištěna tím, že připojení k lince SCL jsou provedena podle principu "AND".

Master nemá výhradní právo řídit přechod SCL linie z nízké do vysoké.Pokud slave potřebuje více času na zpracování přijatého bitu, může nezávisle udržovat SCL na nízké úrovni, dokud není připraven přijmout další bit dat. Linka SCL v takové situaci bude nízká po dobu trvání nejdelšího synchronizačního pulzu nízké úrovně.

Zařízení s nejnižším trvalým minimem zůstanou nečinná, dokud neskončí dlouhé období. Když všechna zařízení dokončí období synchronizace s nízkou úrovní, SCL se zvýší.

Všechna zařízení začnou taktovat vysoko a první zařízení, které dokončí periodu, bude první, které nastaví linku SCL na nízkou úroveň. V důsledku toho bude trvání nízkého stavu SCL určeno nejdelším nízkým stavem synchronizačního impulsu jednoho ze zařízení a trvání vysokého stavu bude určeno nejkratší periodou synchronizace jednoho ze zařízení. zařízení.

Synchronizační signály mohou být použity přijímači jako prostředek pro řízení přenosu dat na bitové a bytové úrovni.

Pokud je zařízení schopno přijímat bajty vysokou rychlostí, ale trvá určitou dobu, než přijatý bajt uloží nebo se připraví na příjem dalšího bajtu, může po přijetí a potvrzení bajtu nadále držet SCL na nízké úrovni, což vynutí vysílač do pohotovostního stavu.

Mikrokontrolér bez vestavěných hardwarových obvodů, například na bitové úrovni, může zpomalit rychlost hodin prodloužením doby jejich nízkého stavu. V důsledku toho bude přenosová rychlost hlavního zařízení určena rychlostí pomalejší zařízení.

ADRESOVÁNÍ

Každé zařízení připojené na sběrnici I2C má jedinečnou programovou adresu, na kterou jej master osloví odesláním specifického příkazu. Mikroobvody stejného typu se vyznačují voličem adres, realizovaným buď ve formě digitálních vstupů voliče, nebo v analogové podobě. Adresy jsou rozděleny do adresního prostoru zařízení připojených ke sběrnici.

Normální režim předpokládá sedmibitové adresování. Adresování funguje následovně: po příkazu «START» master odešle první bajt, který určuje, které slave zařízení je potřeba pro komunikaci s masterem. Existuje také společná volací adresa, která definuje všechna zařízení na sběrnici, všechna zařízení na ni (teoreticky) reagují potvrzením, ale v praxi je to vzácné.

Takže prvních sedm bitů prvního bajtu je adresa slave. Nejméně významný bit, osmý, udává směr odesílání dat. Pokud je zde «0», pak budou informace zapsány z masteru do tohoto slave. Pokud je «1», informace budou čteny masterem z tohoto slave.

Poté, co master dokončí odesílání bajtu adresy, každý slave s ním porovná svou adresu. Každý se stejnou adresou je slave a je definován jako slave vysílač nebo slave přijímač, v závislosti na hodnotě nejméně významného bitu bajtu adresy.

Podřízená adresa může obsahovat pevné a programovatelné části. Poměrně často pracuje v jednom systému velké množství zařízení stejného typu, pak programovatelná část adresy umožňuje použití maximálně stejného typu zařízení na sběrnici. Kolik bitů v bajtu adresy je programovatelných, závisí na počtu volných pinů na čipu.

Někdy stačí pin s analogovým nastavením programovatelného rozsahu adres, například SAA1064 - ovladač LED indikátoru, který má přesně takovou implementaci. Potenciál konkrétního pinu určuje offset adresního prostoru čipu tak, aby čipy stejného typu nebyly v konfliktu pracující na stejné sběrnici. Všechny čipy podporující I2C sběrnici obsahují sadu adres, které výrobce uvádí v dokumentaci.

Kombinace «11110XX» je vyhrazena pro 10bitové adresování. Pokud si představíme výměnu dat z příkazu «START» do příkazu «STOP», bude to vypadat takto:

Jsou zde povoleny jednoduché a kombinované formáty výměny dat. Kombinovaný formát znamená, že mezi «START» a «STOP» mohou master a slave fungovat jako přijímače a vysílače, což je užitečné například při správě sériové paměti.

Nechte první bajt dat přenést adresu paměti. Poté opakováním příkazu «START» a načtením adresy podřízeného zařízení budou data paměti fungovat. Rozhodnutí o automatickém zvýšení nebo snížení adresy, ke které se dříve přistupovalo, činí vývojář zařízení po předchozím prostudování dokumentace k čipu. Tak či onak, po obdržení příkazu START musí všechna zařízení obnovit svou logiku a připravit se na to, že adresa bude nyní pojmenována.